## Table des matières

|                                                                                     |           |

|-------------------------------------------------------------------------------------|-----------|

| <b>1 La logique combinatoire</b>                                                    | <b>1</b>  |

| 1.1 Les portes logiques fondamentales . . . . .                                     | 1         |

| 1.2 Propriétés générales des opérateurs. . . . .                                    | 3         |

| <b>2 La logique séquentielle et stabilité</b>                                       | <b>5</b>  |

| 2.1 Rétroaction et circuits astables . . . . .                                      | 5         |

| 2.2 Un exemple de circuit monostable : le convertisseur tension-fréquence . . . . . | 6         |

| 2.3 Mémoire Set-Reset . . . . .                                                     | 8         |

| <b>3 Pour aller plus loin...</b>                                                    | <b>11</b> |

Dans les chapitres d'électronique, l'information (fournie par un capteur) à transmettre et à transformer (par filtrage par exemple) est représentée par une tension variable au cours du temps, qui peut prendre toute valeur dans une plage considérée. C'est le domaine de l'électronique analogique.

L'électronique logique (ou digitale) fait appel à un codage de l'information et n'utilise que deux états électriques nettement séparables : Haut et Bas, qui représenteront les chiffres 1 et 0 (en logique binaire).

Cette manière de transmettre l'information présente une grande immunité aux parasites (bruit, déformation du signal) puisqu'il suffit de reconnaître, non pas la forme du signal mais des niveaux électriques nettement séparés. Par exemple, une tension supérieure à 3 V sera interprétée comme le chiffre 1, une tension inférieure à 0.5 V représentant le chiffre 0 et on s'arrange pour qu'il ne puisse pas y avoir de valeurs de tensions comprises entre ces deux valeurs.

La manipulation de cette information fait appel à des fonctions logiques qui vérifient les relations de l'algèbre de Boole. Toute variable ne pouvant prendre que les valeurs 0 ou 1 représente un bit (*binary unit of information*). Cette variable peut être l'état d'un système physique, par exemple le fait qu'un interrupteur soit ouvert ou fermé, qu'une tension soit supérieure ou inférieure à une autre... Ce peut être également un des chiffres qui représentent, en base 2, la valeur numérique d'une grandeur physique. Par exemple, le nombre 13 en base 10 s'écrit 1101 en base binaire : il faut donc quatre bits pour le représenter.

## 1 La logique combinatoire

**Définition.** La **logique combinatoire** correspond à l'ensemble des opérations logiques pour lesquelles l'état de sortie ne dépend que des variables d'entrées.

### 1.1 Les portes logiques fondamentales

Les portes logiques électroniques sont fondamentalement configurées et mises en œuvre à l'aide de blocs semi-conducteurs ou d'éléments tels que des diodes ou des transistors qui fonctionnent comme des commutateurs MARCHE/ARRÊT ayant un motif de commutation bien défini. On parle d'**interrupteurs commandés en tension**. Ces interrupteurs commandés, s'ils sont ouverts, permettent l'accès à l'état binaire 1 alors que, s'ils sont fermés, permettent l'accès à l'état binaire 0.

| La physique des éléments internes aux portes logiques n'est pas un domaine d'étude de ce programme.

**Propriété.** Les portes idéales sont d'impédance d'entrée infinie, les courants d'entrée sont nuls.

Cela facilite la mise en cascade des portes de telle sorte qu'elle permet facilement la composition de fonctions booléennes, ce qui permet de créer des modèles physiques de toute la logique booléenne. Cela permet en outre des algorithmes et des mathématiques inscriptibles à l'aide de la logique booléenne.

### 1.1.1 La porte NOT

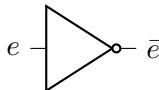

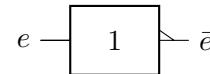

L'opérateur NOT agit sur une seule variable d'entrée  $e$ . La porte renvoie l'opposé de celui-ci, noté usuellement  $\bar{e}$ . En français, on désigne cet opérateur par NON.

Les représentations de la porte NOT sont représentées figure 1. Le premier aux formes arrondies est normalisé par l'ANSI (*American National Standard Institute*). Il est très utilisé en Amérique du Nord. Le second, aux formes à angles droits, est plus riche en détails et est surtout utilisé pour représenter des circuits complexes. Il est normalisé par l'IEC (*International Technical Comission*). Ce symbolisme est largement utilisé en Europe. Les numériciens préfèrent utiliser le premier, d'autant plus qu'on le trouve également dans les logiciels de conception numérique.

(a) Représentation américaine (ANSI)

(b) Représentation européenne (IEC)

**Fig. 1 – Représentations schématiques de la porte NOT**

**Définition.** Une table de vérité est un tableau comportant plusieurs colonnes. Les valeurs des cellules de ce tableau sont appelées « valeurs de vérité » (1 ou V pour vrai, 0 ou F pour faux) en mathématiques, et « états logiques » (1 ou V pour activé, 0 ou F pour désactivé) en électronique.

La table de vérité de la porte NOT est évidemment très simple et est représentée table 1.

| $e$ | $\bar{e}$ |

|-----|-----------|

| 1   | 0         |

| 0   | 1         |

**Tab. 1 – Table de vérité de la porte NOT**

### 1.1.2 La porte AND

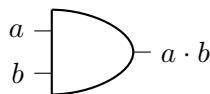

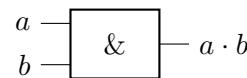

L'opérateur AND agit sur deux variables d'entrées  $a$  et  $b$ . La porte renvoie 1 uniquement si les deux entrées valent 1. On note sa sortie  $a \cdot b$ . Sa table de vérité est représentée table 2. Les représentations de la porte AND sont représentées figure 2. En français, on désigne cet opérateur par ET.

| $a$ | $b$ | $a \cdot b$ |

|-----|-----|-------------|

| 0   | 0   | 0           |

| 1   | 0   | 0           |

| 0   | 1   | 0           |

| 1   | 1   | 1           |

**Tab. 2 – Table de vérité de la porte AND**

(a) Représentation américaine (ANSI)

(b) Représentation européenne (IEC)

**Fig. 2 – Représentations schématiques de la porte AND**

Certaines portes électroniques permettent d'utiliser la fonction AND sur plus de deux entrées. Dans ce cas, elle ne renvoie 1 que si toutes les entrées sont à 1.

### 1.1.3 La porte OR

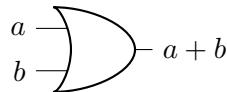

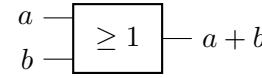

L'opérateur OR agit sur deux variables d'entrées  $a$  et  $b$ . La porte renvoie 1 si l'une ou l'autre ou les deux entrées valent 1. On note sa sortie  $a + b$ . Sa table de vérité est représentée table 3. Les représentations de la porte OR sont représentées figure 3. En français, on désigne cet opérateur par OU.

| $a$ | $b$ | $a + b$ |

|-----|-----|---------|

| 0   | 0   | 0       |

| 1   | 0   | 1       |

| 0   | 1   | 1       |

| 1   | 1   | 1       |

**Tab. 3 – Table de vérité de la porte OR**

(a) Représentation américaine (ANSI)

(b) Représentation européenne (IEC)

**Fig. 3 – Représentations schématiques de la porte OR**

Certaines portes électroniques permettent d'utiliser la fonction OR sur plus de deux entrées. Dans ce cas, elle ne renvoie 1 que si au moins une des entrées est à 1.

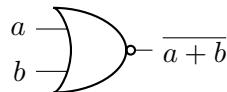

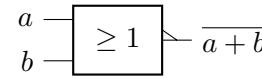

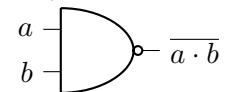

### 1.1.4 Les opérateurs inverseurs

L'opérateur inverseur permet de combiner directement une porte avec la fonction NOT. La représentation est celle de la porte originale à laquelle on rajoute le symbole du NOT : un petit rond en norme ANSI ou un petit triangle en norme IEC.

Sans entrer dans les détails techniques et historiques, il s'avérait que fabriquer des portes inverseuses était plus facile et plus économique que des portes non inverseuses. De plus, le fait de travailler essentiellement avec des portes inverseuses permettait aux industriels d'avoir un stock moins important de composants différents. On les retrouvera donc plus souvent dans les circuits électroniques. Ces raisons historiques n'ont plus lieu d'être car on utilise essentiellement des circuits intégrés programmables, mais ces opérateurs restent encore très présents.

Les tables de vérités des portes NOR et NAND sont représentées table 4. Les représentations des portes NOR et NAND sont représentées figure 4. En français, on désigne ces opérateurs par NON OU et NON ET.

(a) Porte NOR : représentation américaine (ANSI)

(b) Porte NOR : représentation européenne (IEC)

(c) Porte NAND : représentation américaine (ANSI)

(d) Porte NAND : représentation européenne (IEC)

**Fig. 4 – Représentations schématiques des portes NOR et NAND**

## 1.2 Propriétés générales des opérateurs

### 1.2.1 L'algèbre de Boole

L'algèbre de Boole est constitué des deux éléments : 1 et 0. On peut utiliser trois opérations : la négation, l'addition et la multiplication tels que définis par les opérateurs NOT, OR et AND.

| $a$ | $b$ | $a + b$ | $\bar{a} + \bar{b}$ | $a \cdot b$ | $a \cdot \bar{b}$ |

|-----|-----|---------|---------------------|-------------|-------------------|

| 0   | 0   | 0       | 1                   | 0           | 1                 |

| 1   | 0   | 1       | 0                   | 0           | 1                 |

| 0   | 1   | 1       | 0                   | 0           | 1                 |

| 1   | 1   | 1       | 0                   | 1           | 0                 |

**Tab. 4 – Table de vérité des portes NOR et NAND**

**Propriété.** Pour montrer une égalité dans l'algèbre de Boole, il suffit de tracer les tables de vérités des deux termes et de constater l'égalité.

Par exemple, on a les égalités suivantes  $a + 0 = a$ ,  $a + 1 = 1$ ,  $a \cdot 0 = 0$  et  $a \cdot 1 = a$  justifiées par la table de vérité ci-dessous.

| $a$ | 1 | 0 | $a + 0$ | $a + 1$ | $a \cdot 0$ | $a \cdot 1$ |

|-----|---|---|---------|---------|-------------|-------------|

| 0   | 1 | 0 | 0       | 1       | 0           | 0           |

| 1   | 1 | 0 | 1       | 1       | 0           | 1           |

On constate que 1 est neutre pour  $\cdot$  et absorbant pour  $+$  alors que c'est l'inverse pour 0.

On peut de plus montrer que ces opérations sont associatives, distributives et commutatives.

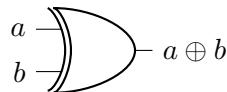

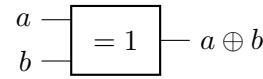

### 1.2.2 La porte XOR

L'opérateur XOR agit sur deux variables d'entrées  $a$  et  $b$ . La porte renvoie 1 si l'une ou l'autre (mais pas les deux) valent 1. On note sa sortie  $a \oplus b$ . Sa table de vérité est représentée table 5. Les représentations de la porte XOR sont représentées figure 5. En français, on désigne cet opérateur par OU EXCLUSIF.

| $a$ | $b$ | $a \oplus b$ |

|-----|-----|--------------|

| 0   | 0   | 0            |

| 1   | 0   | 1            |

| 0   | 1   | 1            |

| 1   | 1   | 0            |

**Tab. 5 – Table de vérité de la porte XOR**

(a) Représentation américaine (ANSI)

(b) Représentation européenne (IEC)

**Fig. 5 – Représentations schématiques de la porte XOR**

Le XOR n'est pas une opération fondamentale. Ainsi, il est possible de le construire comme une combinaison des autres opérations. On montre en effet avec la table de vérité ci-dessous que

$$a \oplus b = \bar{b} \cdot a + b \cdot \bar{a} .$$

| $a$ | $b$ | $a \oplus b$ | $\bar{a}$ | $\bar{b}$ | $\bar{b} \cdot a$ | $b \cdot \bar{a}$ | $\bar{b} \cdot a + b \cdot \bar{a}$ |

|-----|-----|--------------|-----------|-----------|-------------------|-------------------|-------------------------------------|

| 0   | 0   | 0            | 1         | 1         | 0                 | 0                 | 0                                   |

| 1   | 0   | 1            | 0         | 1         | 1                 | 0                 | 1                                   |

| 0   | 1   | 1            | 1         | 0         | 0                 | 1                 | 1                                   |

| 1   | 1   | 0            | 0         | 0         | 0                 | 0                 | 0                                   |

On définit aussi par ailleurs l'opérateur XNOR comme l'opérateur inverse du XOR. On note alors  $\overline{a \oplus b} = a \odot b$ .

### 1.2.3 Les lois de de Morgan

**Propriété.** Les lois de de Morgan indiquent

$$a + \bar{b} = \bar{a} \cdot \bar{b} \quad \text{et} \quad \bar{a} \cdot \bar{b} = \bar{a} + \bar{b} .$$

Ces relations établissent le lien entre les trois opérateurs fondamentaux.

La démonstration de ces relations passe par la table de vérité ci-dessous.

| $a$ | $b$ | $\bar{a}$ | $\bar{b}$ | $a + b$ | $\bar{a} + \bar{b}$ | $\bar{a} \cdot \bar{b}$ | $a \cdot b$ | $\bar{a} \cdot \bar{b}$ | $\bar{a} + \bar{b}$ |

|-----|-----|-----------|-----------|---------|---------------------|-------------------------|-------------|-------------------------|---------------------|

| 0   | 0   | 1         | 1         | 0       | 1                   | 1                       | 0           | 1                       | 1                   |

| 1   | 0   | 0         | 1         | 1       | 0                   | 0                       | 0           | 1                       | 1                   |

| 0   | 1   | 1         | 0         | 1       | 0                   | 0                       | 0           | 1                       | 1                   |

| 1   | 1   | 0         | 0         | 1       | 0                   | 0                       | 1           | 0                       | 0                   |

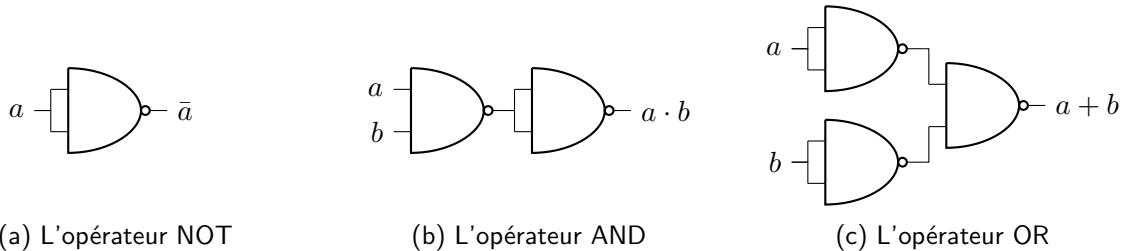

À partir de ces relations, on montre que l'on peut utiliser la seule porte NAND pour réaliser toutes les opérations.

En effet, on a note, la sortie d'une porte NAND est  $\bar{a} \cdot \bar{b}$ .

La porte NOT se construit avec  $\bar{a} \cdot \bar{a} = \bar{a} + \bar{a} = \bar{a}$ . On en déduit la porte AND par une négation de la porte NAND  $\bar{a} \cdot \bar{b} = a \cdot b$ . Et pour OR, on réalise l'opération cette fois avec 3 portes NAND via la relation  $\bar{a} \cdot \bar{\bar{b}} = \bar{a} + \bar{b} = a + b$ .

Les circuits correspondant sont représentés figure 6.

**Fig. 6 – Opérateurs élémentaires uniquement avec la porte NAND**

Un résultat identique s'applique avec les portes NOR.

**Propriété.** Tous les circuits peuvent être exclusivement réalisés avec des portes NAND ou des portes NOR. On dit que ces opérateurs forment chacun un groupe logique complet.

## 2 La logique séquentielle et stabilité

### 2.1 Rétroaction et circuits astables

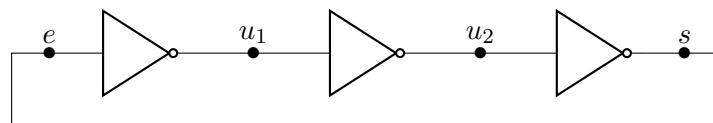

Considérons le circuit de la figure 7.

**Fig. 7 – Circuit astable composé de portes NOT.**

On a  $u_1 = \bar{e}$ ,  $u_2 = \bar{u}_1 = e$  et  $s = \bar{u}_2 = \bar{e}$ . Cette dernière relation est impossible en logique formelle car, le système étant bouclé, on a  $s = e$ .

En réalité, le caractère réel et physique des portes implique une commutation non instantanée. Ainsi, celle-ci prend un certain temps, noté  $\tau$ , pour apparaître. Ainsi, quand la troisième bascule a lieu, la valeur

d'entrée  $e(3\tau)$  est différente de la valeur initiale  $e(0)$ . Pour revenir à la valeur initiale pour la valeur d'entrée, il faut donc attendre le temps  $6\tau$ , qui correspond à deux fois le temps nécessaire à la commutation des 3 portes. Cette oscillation est permanente car le système est toujours en état instable. Ce n'est pas le cas si on utilise un nombre pair de portes NOT.

**Définition.** Un système bouclé est dit **astable** s'il n'y a pas d'état stable du système.

### 2.1.1 La logique séquentielle

**Définition.** Un système séquentiel voit sa sortie évoluer non seulement en fonction des entrées, mais également en fonction de la valeur de sortie de celui-ci. Il s'agit d'un système bouclé pour lequel la sortie est réinjectée dans le système.

L'évolution du système est intrinsèquement liée au temps de commutation des portes logiques, ce temps étant intrinsèquement lié au processus physique de celles-ci ainsi qu'au choix des fabricants. Ce temps est souvent mal contrôlé, il dépend en effet du nombre de composants dans le circuit. On préfère donc toujours utiliser une horloge externe aux composants logiques. Celle-ci aura pour but de synchroniser l'ensemble des composants à travers le circuit. L'horloge est ainsi le signal le plus important dans un circuit numérique.

Les circuits séquentiels actuels sont majoritairement basées sur des objets appelés « bascule D ». Celle-ci garde en mémoire une valeur binaire sauf à certains instants imposés par l'horloge. À ces instants précis, selon la commande de la bascule D, la valeur gardée en mémoire peut être modifiée. Ces composants, essentiels en électronique moderne, ne sont pas étudiés au programme de MPI.

## 2.2 Un exemple de circuit monostable : le convertisseur tension-fréquence

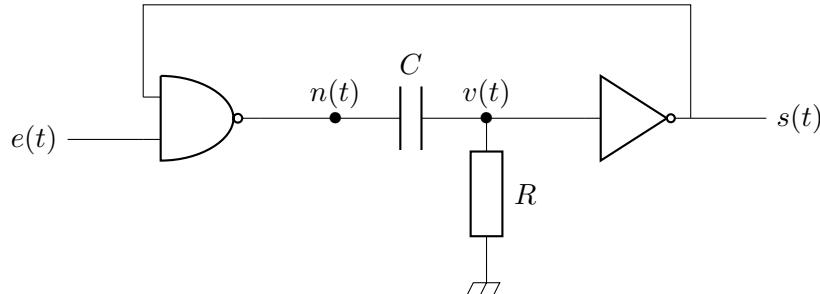

On étudie le convertisseur tension-fréquence représenté figure 8.

**Fig. 8** – Convertisseur tension-fréquence.

### 2.2.1 Étude du filtre

La relation entre  $n(t)$  et  $v(t)$  se déduit de l'étude en régime complexe à l'aide d'un pont diviseur, il vient donc

$$\underline{v} = \frac{R}{R + 1/(jC\omega)} \underline{n} \quad \Rightarrow \quad \underline{n} = \underline{v} + \frac{1}{RC} \frac{\underline{v}}{j\omega}.$$

Pour utiliser le pont diviseur, il est nécessaire que le courant d'entrée la porte soit nul. C'est le cas grâce à l'impédance d'entrée de la porte supposée infinie.

En revenant en temporel, on a donc

$$\frac{dv}{dt}(t) + \frac{1}{\tau} v(t) = \frac{dn}{dt}(t) = 0 \tag{2.1}$$

où on note  $\tau = RC$  la constante de temps de l'intégrateur. La tension  $n$  est de dérivée nulle car, en sortie d'une porte logique, elle vaut soit l'état 0, soit l'état haut sans varier en dehors des bascules.

On remarque que la tension aux bornes du condensateur vaut  $v(t) - n(t)$ . Cette différence de tension est une fonction continue du temps.

### 2.2.2 Étude temporelle de la tension de sortie

**Supposons que l'entrée vérifie  $e(t) = e_0$  depuis un certain temps, correspondant à la tension de l'état haut.** Faisons l'hypothèse qu'un régime stationnaire est atteint. Cette hypothèse n'est pas évidente car on a vu dans l'exemple du circuit astable que des oscillations pouvaient apparaître.

Sous cette hypothèse, comme vu précédemment, la tension  $v$  vérifie une équation différentielle d'ordre 1 à coefficients constants et à second membre nul. Donc au bout d'un certain temps, soit au minimum  $5\tau$ , on a  $v = 0$ .

Or  $s = \bar{v}$  donc la sortie  $s$  vaut  $e_0$ . Ainsi, les deux entrée de la porte NAND valent  $e_0$ , on a nécessairement  $n = 0$ . Le condensateur est donc déchargé car  $q = C(n - v)$  et  $n = v = 0$ .

L'hypothèse de régime stationnaire est donc cohérente avec les conséquences de celle-ci. La logique formelle n'est pas mise en défaut par le caractère réel des portes.

Ainsi, l'état de sortie  $s = e_0$  reste constant.

**Supposons qu'à  $t = 0$ , l'entrée bascule à 0 pendant le temps  $T$ .** Dans ce cas,  $n(0) = e_0$  car au moins une des deux entrées de la porte NAND est nulle. La tension aux bornes du condensateur étant continue, on a immédiatement  $v(0) = e_0$ . La sortie du système passe donc à 0 et les deux entrées de la porte NAND sont nulles.

Toutefois, au vu de l'équation différentielle (2.1), on en déduit que  $v(t) = e_0 \exp(-t/\tau)$ . Le condensateur se charge donc car les potentiels à ses bornes sont différents. La charge du condensateur se poursuit tant que la sortie de porte NAND ne change pas, soit tant que les deux entrées ne sont pas égales à 1.

Ainsi, la tension  $v(t)$  décroît exponentiellement.

Supposons que la bascule de la porte NOT se fasse pour  $e_0/2$ , dans ce cas l'état de sortie  $v_s$  passe de 0 à  $e_0$  lorsque  $v(t)$  atteint la valeur  $e_0/2$ , soit le temps de bascule  $T_B = \tau \ln 2$ .

Il existe deux possibilité :

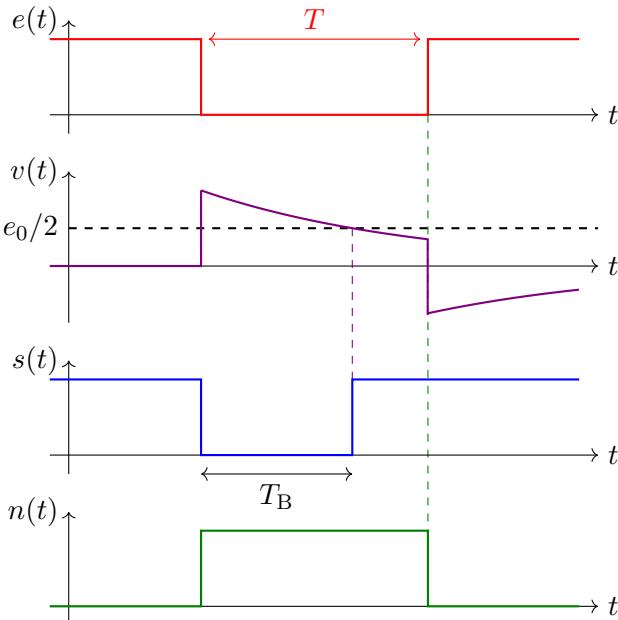

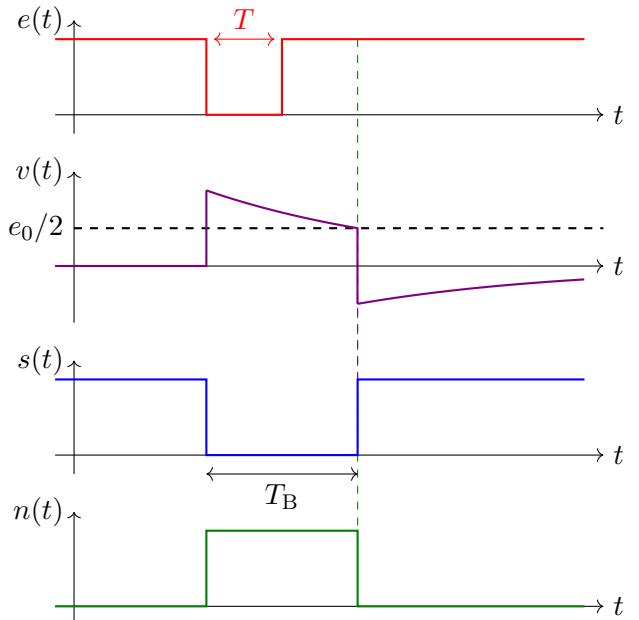

- ▷  $T > T_B$  : l'entrée est toujours à 0 alors que la sortie est passé de 0 à 1 (état logique) au bout du temps  $T_B$  ;

- ▷  $T < T_B$  : l'entrée est repassée à 1, mais la seconde entrée de la porte NAND n'a pas encore basculé à 1 car il est nécessaire d'attendre  $T_B$ .

La bascule de la sortie entre 0 et 1 est donc imposée uniquement par la charge du condensateur. L'état de sortie 0 est donc un état instable de durée  $T_B$ , quelle que soit la durée du passage à 0 de la tension d'entrée.

**Supposons que l'entrée vérifie  $e(t) = e_0$  depuis un temps court.** L'entrée vient de changer de valeur. On est dans la poursuite de la phase précédente. La charge du condensateur se poursuit tant que  $n$  n'a pas changé de valeur. Notons  $t_0$  l'instant de cette bascule. Par continuité de  $n - v$ , il vient  $n(t_0^+) - v(t_0^-) = n(t_0^-) - v(t_0^+)$  soit  $v(t_0^+) = v(t_0^-) - e_0 < 0$ . La tension  $v$  est alors négative et tend à nouveau exponentiellement vers 0. Le condensateur se décharge donc.

La tension  $v$  étant négative, la sortie vaut  $e_0$ . Ainsi, dès que l'entrée vaut  $e_0$ , on a toujours  $s = e_0$ .

### 2.2.3 Chronogramme

**Définition.** Un système séquentiel **monostable** est un système présentant un état stable dans lequel il peut rester indéfiniment et un état instable de durée déterminée (période).

Ce système est donc monostable, ce qui se visualise plus simplement dans le tracé des chronogrammes de la figure 9.

**Remarque :** Pour que les résultats soit bien vérifiés, il faut que, entre deux bascules de  $e$  vers 0, le condensateur ait eu le temps de se décharger complètement. Cette hypothèse impose une contrainte sur la fréquence du signal d'entrée.

Pour revenir à la moyenne, on réalise un nouveau montage où on utilise une porte NOT suivi d'un filtre moyenneur (par exemple un passe bas de fréquence bien choisie) en sortie de montage.

(a) Le signal d'entrée change de valeur sur une durée plus longue que la bascule

(b) Le signal d'entrée change de valeur sur une durée plus courte que la bascule

**Fig. 9** – Tracé des différentes tensions d'entrées en fonction du temps. On remarque que quelle que soit la durée du changement d'état de l'entrée, la sortie ne peut être sur l'état 0 que sur une durée fixe et définie. L'état 0 de la sortie est de durée constante. L'état stable de la sortie est l'état haut. La sortie  $n$  de la porte NAND est dans l'état haut lorsque les deux entrées le sont aussi.

En effet, prenons un signal périodique de période  $T$  dépassant en entrée une fois pendant son cycle la valeur  $e_0$ . La sortie  $s$  vaut 0 pendant la durée  $T_B$  et  $e_0$  pendant la durée  $T - T_B$ . Derrière la porte NOT, on a l'inverse, soit un signal créneau valant 0 pendant la durée  $T - T_B$  et  $e_0$  pendant la durée  $T_B$ . La moyenne de ce signal créneau est donc directement  $\langle \bar{s} \rangle = e_0 T_B / T = e_0 T_B f$ . Ainsi, la tension de sortie proportionnelle à la fréquence du signal d'entrée.

## 2.3 Mémoire Set-Reset

Il s'agit de la bascule RS. Ce montage n'est plus utilisé en pratique mais a eu une grande importance historique et est accessible avec les éléments de ce cours.

Il s'agit du circuit séquentiel le plus simple et le plus fondamental.

### 2.3.1 Principe

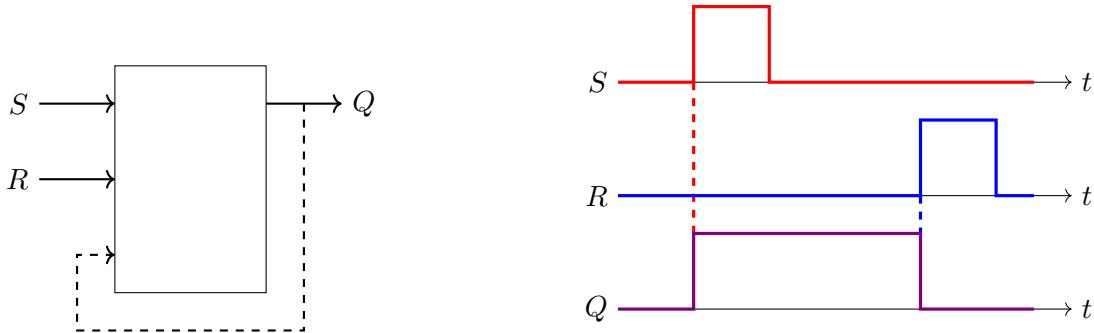

Une bascule RS a deux entrées : l'entrée « Set » notée ( $S$ ) et l'entrée « Reset » notée ( $R$ ). La sortie du circuit est notée  $Q$ . Le principe est schématisé figure 10 :

- ▷ lorsque l'entrée  $S$  passe à 1, la sortie  $Q$  passe à 1 ;

- ▷ cette sortie reste à 1 quelle que soit la valeur de  $S$  ;

- ▷ lorsque l'entrée  $R$  passe à 1, la sortie  $Q$  passe à 0.

Le cas  $R = S = 1$  n'est normalement pas possible dans les utilisations normales de la bascule RS.

**Fig. 10** – Principe de la mémoire Set-Reset et chronogramme des différentes grandeurs électriques

### 2.3.2 Équation

Au vu de la figure 10, on constate la logique séquentielle du circuit. En effet, on se rend compte que pour  $S = R = 0$ , la sortie  $Q$  peut prendre la valeur 0 ou 1 selon l'histoire du circuit. Ce n'est pas possible pour un système combinatoire. C'est ce qui constitue « l'effet mémoire ».

Pour écrire une équation combinatoire de la sortie, on doit différencier les deux états  $S = R = 0$  ayant la valeur 0 pour  $Q = 0$  et ayant la valeur 1 pour  $Q = 1$ . Le variable  $Q$  permet donc de différencier ces deux états. L'équation du Set-Reset est donc une relation combinatoire de la forme

$$Q_+ = f(R, S, Q_-)$$

où  $Q_+$  et la valeur de  $Q$  après la modification de l'entrée et  $Q_-$  la valeur de  $Q$  avant la modification de l'entrée.

La table de vérité souhaitée correspondant à cette équation est donnée tableau 6.

| $S$ | $R$ | $Q_-$ | $Q_+$ |

|-----|-----|-------|-------|

| 0   | 0   | 0     | 0     |

| 0   | 0   | 1     | 1     |

| 0   | 1   | 0     | 0     |

| 0   | 1   | 1     | 0     |

| 1   | 0   | 0     | 1     |

| 1   | 0   | 1     | 1     |

**Tab. 6** – Table de vérité correspondant au fonctionnement souhaité de la bascule RS. Le cas  $R = S = 1$  n'est normalement pas possible dans les utilisations normales de la bascule RS, il n'est donc pas représenté.

**Définition.** Un système séquentiel **bistable** est un système présentant deux états stables. Ils peuvent passer d'un état à l'autre par une impulsion extérieure de commande.

On constate que la bascule RS est un système bistable. Le changement de valeur de  $Q$  étant lié à une combinaison particulière des valeurs d'entrées.

### 2.3.3 Réalisations pratiques

La table de vérité du tableau 6 ne permet pas de décrire entièrement un circuit logique. En effet, comme le cas  $R = S = 1$  est laissé libre, plusieurs possibilités de circuits logiques sont possibles.

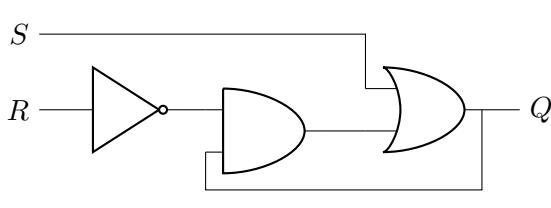

**Mémoire à inscription prioritaire :** elle favorise l'inscription S sur l'effacement R. Dans ce cas,  $S = R = 1$  implique  $Q_+ = 1$ . Elle est définie par la relation

$$Q_+ = S + \bar{R} \cdot Q_- . \quad (2.2)$$

Cette relation vérifie donc  $Q_+ = 1$  dès que  $S = 1$ . Elle vérifie de plus le reste de la table de vérité du tableau 6.

La réalisation directe de cette porte est réalisé figure 11a et son équivalent avec des portes NAND est donnée figure 11b.

(a) Circuit directement issu de la fonction logique (2.2).

(b) Circuit équivalent à portes NAND.

**Fig. 11 – Bascule RS à inscription prioritaire**

Les circuits des figures 11a et 11b sont équivalents. En effet, on utilise l'équivalence de la figure 6a entre les portes NAND et NOT et il vient pour le second circuit

$$Q_+ = \overline{S \cdot (\bar{R} \cdot Q_-)} = S + \bar{R} \cdot Q_-$$

où on utilise la seconde loi de de Morgan.

L'intérêt du circuit équivalent à porte NAND est que la seconde sortie correspond directement à  $\bar{Q}$ . En effet, la sortie de la seconde porte correspond à

$$\overline{Q \cdot \bar{R}} = \bar{Q} + R .$$

Si  $R = 0$ , on a bien  $\bar{Q}$  en sortie et si  $R = 1$ , on a  $\bar{Q} = 1$ . Il s'agit donc bien du résultat souhaité.

**Remarque :** Ce comportement ne fonctionne en réalité pas pour l'inscription prioritaire car  $R = 1$  n'implique pas  $Q = 0$  dans le cas  $S = 1$ . Toutefois, comme la bascule ne se préoccupe pas du cas  $R = S = 1$ , on a bien le résultat voulu pour une bascule RS.

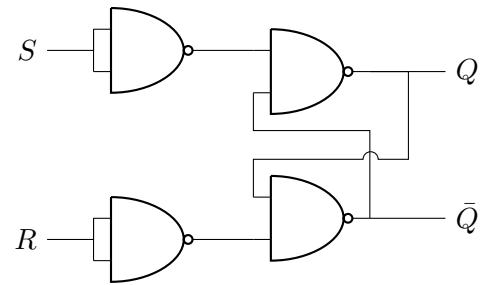

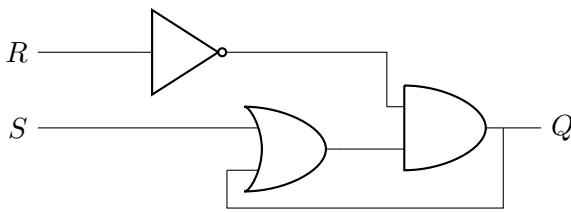

**Mémoire à effacement prioritaire :** elle favorise l'effacement S sur l'inscription R. Dans ce cas,  $S = R = 1$  implique  $Q_+ = 0$ . Elle est définie par la relation

$$Q_+ = \bar{R} \cdot (S + Q_-) . \quad (2.3)$$

Cette relation vérifie donc  $Q_+ = 0$  dès que  $R = 1$ . Elle vérifie de plus le reste de la table de vérité du tableau 6.

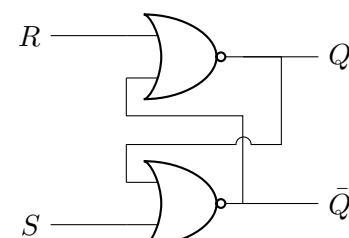

La réalisation directe de cette porte est réalisé figure 12a et son équivalent avec des portes NOR est donnée figure 12b.

(a) Circuit directement issu de la fonction logique (2.3).

(b) Circuit équivalent à portes NOR.

**Fig. 12 – Bascule RS à effacement prioritaire**

Les circuits des figures 12a et 12b sont équivalents. En effet, on a pour le second circuit

$$Q_+ = \overline{R + (\overline{S + Q_-})} = \bar{R} \cdot (S + Q_-)$$

où on utilise la première loi de de Morgan.

L'intérêt du circuit équivalent à porte NOR est que la seconde sortie correspond directement à  $\bar{Q}$ . En effet, la sortie de la seconde porte correspond à

$$\overline{Q + S} = \bar{Q} \cdot \bar{S} .$$

Si  $S = 0$ , on a bien  $\bar{Q}$  en sortie et si  $S = 1$ , on a  $\bar{Q} = 0$ . Il s'agit donc bien du résultat souhaité.

**Remarque :** À nouveau, ce comportement ne fonctionne en réalité pas pour l'effacement prioritaire car  $S = 1$  n'implique pas  $Q = 1$  dans le cas  $R = 1$ . Toutefois, comme la bascule ne se préoccupe pas du cas  $R = S = 1$ , on a bien le résultat générique voulu pour une bascule RS.

### 3 Pour aller plus loin...

Pour aller plus loin, le [site suivant](#) [1] regroupe de nombreux circuits avec lesquels on peut jouer.

## Références

- [1] <http://ressources.univ-lemans.fr/AccesLibre/UM/Pedago/physique/02/mnelectro.html>